LUẬN ÁN CỦA TIẾN SĨ

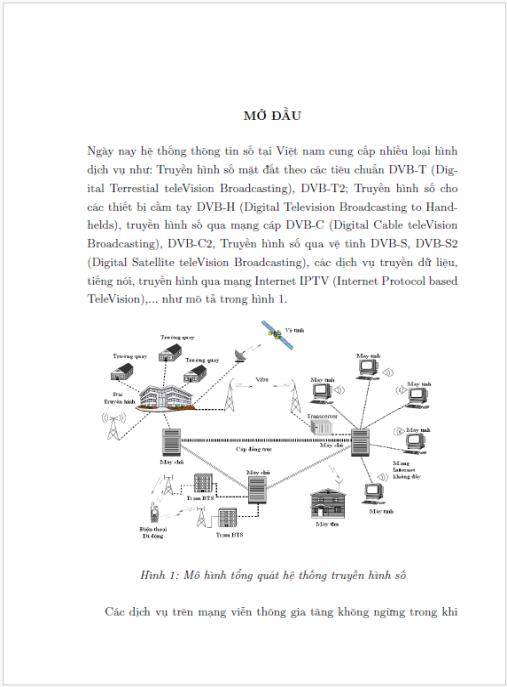

Tên đề tài luận án: Nghiên cứu xây dựng mã sửa sai có ma trận kiểm tra mật độ thấp trong truyền dẫn số.

Chuyên ngành: Kỹ thuật điện tử Mã số: 62.52.02.03

Nghiên cứu sinh: Cao Văn Liết

Tập thể hướng dẫn khoa học: PGS.TS. Nguyễn Hồng Vũ; TS. Nguyễn Thế Truyện

Cơ sở đào tạo: Viện Nghiên cứu Điện tử, Tin học, Tự động hóa.

Thực hiện mục tiêu đề ra, luận văn đã tiến hành nghiên cứu, xây dựng ma trận sinh và ma trận kiểm tra của mã LDPC, nhằm tối ưu khả năng sửa lỗi của mã LDPC, đã xây dựng, tối ưu hóa các mô hình tích hợp giữa mã LDPC với các hệ thống thông tin nhằm tăng khả năng chống lỗi của hệ thống với độ phức tạp phù hợp. Đề tài đã đạt được các kết quả nghiên cứu và có các đóng góp chính sau đây:

1. Xây dựng mối quan hệ đặc biệt giữa ma trận sinh và ma trận kiểm tra của mã LDPC, nhằm giảm độ phức tạp trong quá trình tính toán xây dựng ma trận sinh của mã LDPC truyền thống. Ma trận sinh của mã LDPC được suy trực tiếp từ ma trận kiểm tra.

2. Xây dựng cấu trúc ma trận thành phần của ma trận sinh bằng các hàm phân bố ngẫu nhiên trong hàng và cột, hiệu quả của quá trình xây dựng này là làm tăng khả năng sửa lỗi của mã LDPC so với các mã LDPC phổ thông từ 0,5dB đến 1dB, tùy theo từng điều kiện cụ thể.

3. Xây dựng mô hình lai ghép giữa mã LDPC và ARQ, nhằm tăng cường khả năng chống lỗi do can nhiễu của đường truyền và thông lượng của hệ thống.

4. Xây dựng mô hình tích hợp giữa mã LDPC và hệ thống V-BLAST, nhằm tăng cường khả năng sửa lỗi của hệ thống tốt hơn với 5dB so với mô hình tích hợp mã URC và V-BLAST, tối ưu các thông số trong hệ thống để giảm thiểu độ phức tạp của hệ thống so với hệ thống URC-VBLAST.